This section provides information about the instrument's SCPI programming interface.

Refer to SCPI List for a comprehensive list of all remote commands available for the VXG signal generator.

What Are Status Register SCPI Commands

How to Use the Status Registers

Status Register Bit Parameters

STATus Subsystem Registers and Commands

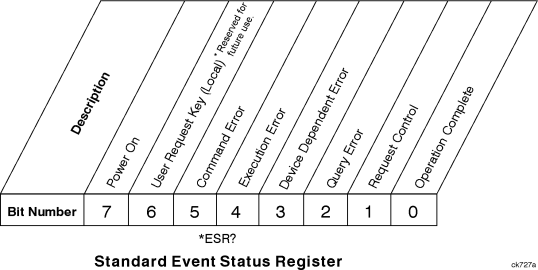

Standard Event Status Register

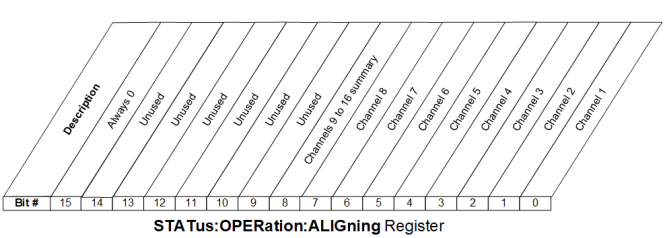

STATus:OPERation:ALIGning Register

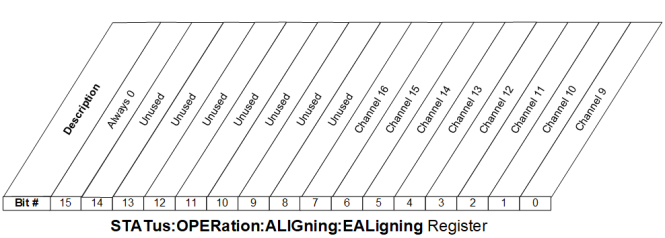

STATus:OPERation:ALIGning:EALigning Register

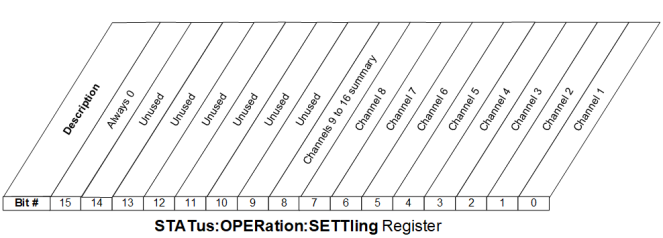

STATus:OPERation:SETTling Register

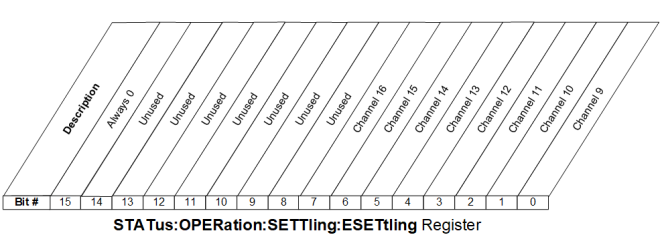

STATus:OPERation:SETTling:ESETtling Register

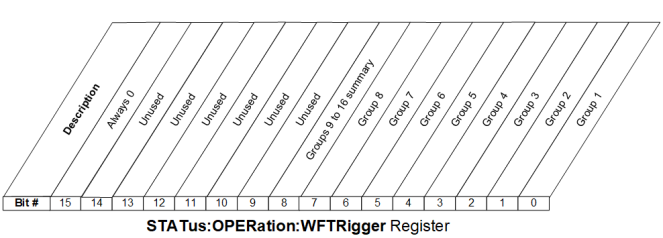

STATus:OPERation:WFTRigger Register

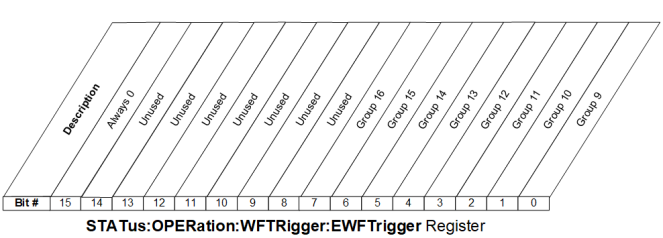

STATus:OPERation:WFTRigger:EWFTrigger Register

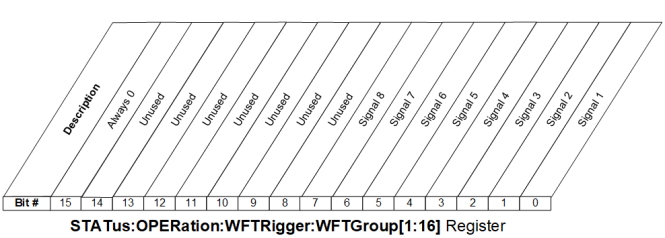

STATus:OPERation:WFTRigger:WFTGroup Registers

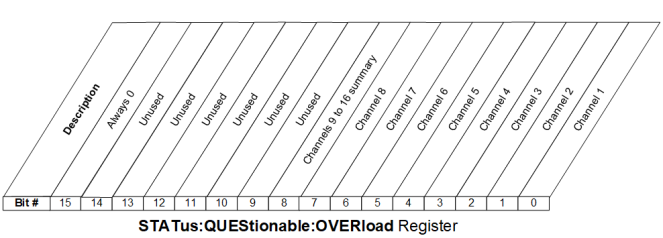

STATus:QUEStionable:OVERload Register

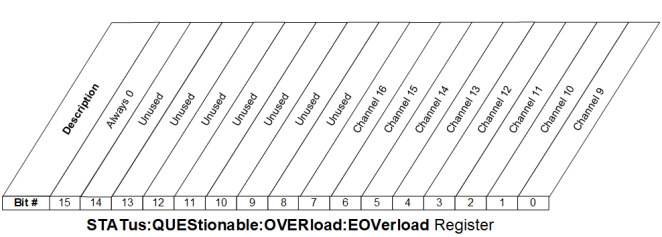

STATus:QUEStionable:OVERload:EOVerload Register

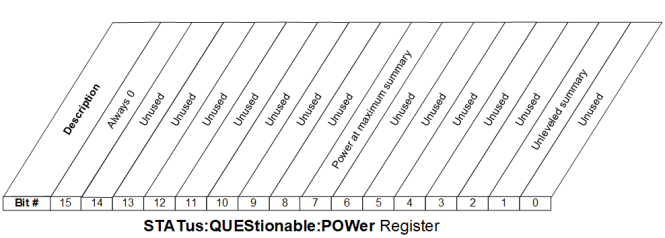

STATus:QUEStionable:POWer Register

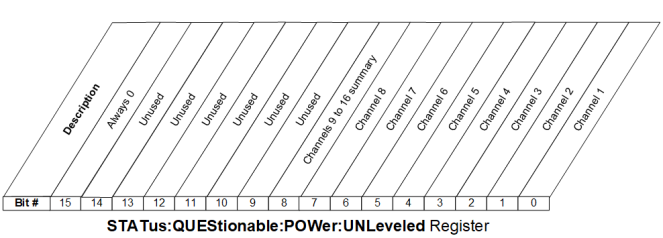

STATus:QUEStionable:POWer:UNLeveled Register

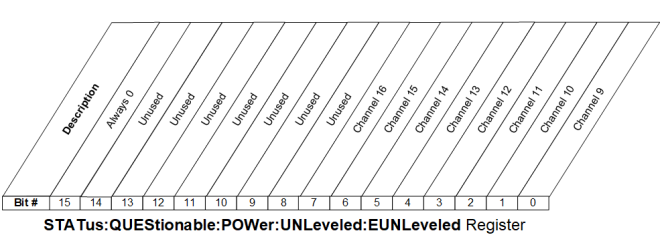

STATus:QUEStionable:POWer:UNLeveled:EUNLeveled Register

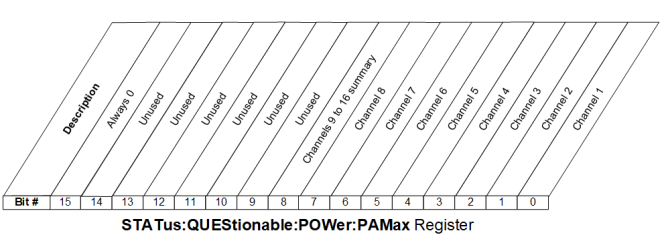

STATus:QUEStionable:POWer:PAMax Register

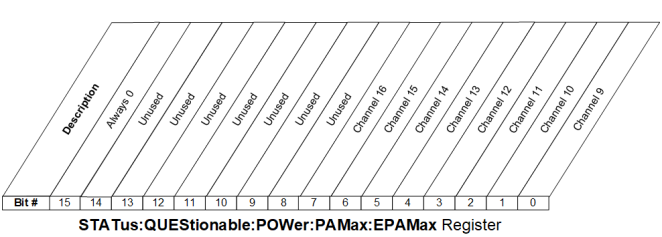

STATus:QUEStionable:POWer:PAMax:EPAMax Register

STATus:QUEStionable:POWer Register

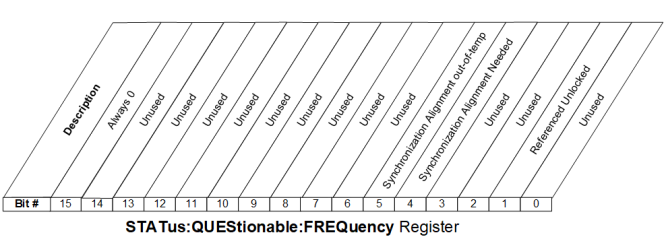

STATus:QUEStionable:FREQuency Register

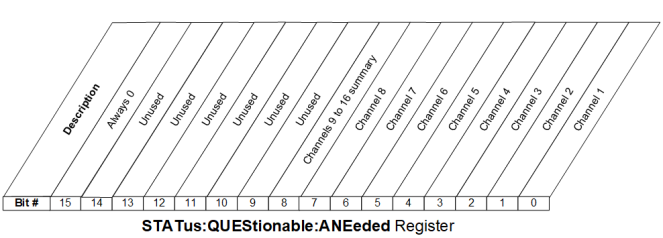

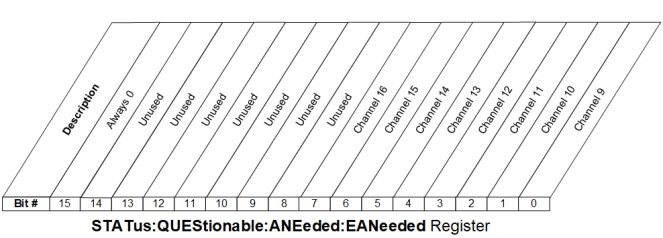

STATus:QUEStionable:ANEeded Register

STATus:QUEStionable:ANEeded:EANeeded Register

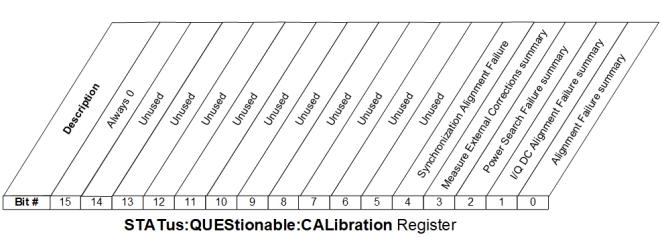

STATus:QUEStionable:CALibration Register

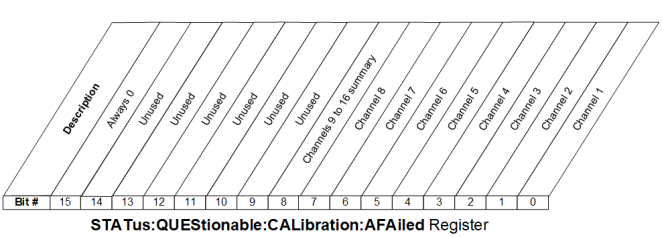

STATus:QUEStionable:CALibration:AFAiled Register

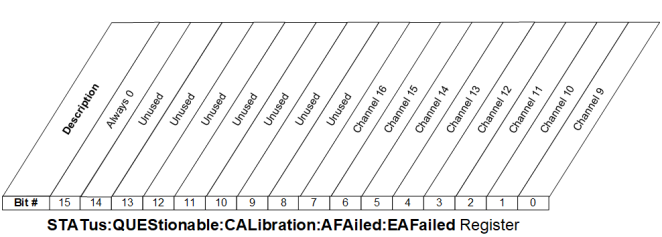

STATus:QUEStionable:CALibration:AFAiled:EAFailed Register

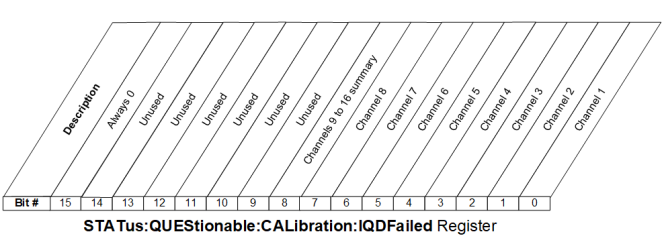

STATus:QUEStionable:CALibration:IQDFailed Register

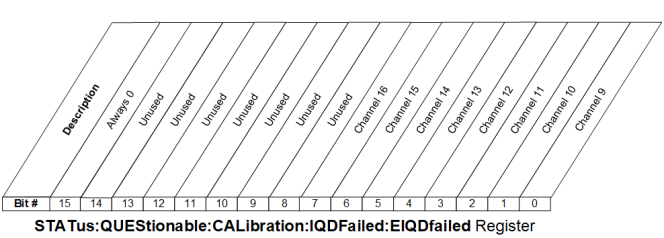

STATus:QUEStionable:CALibration:IQDFailed:EIQDfailed Register

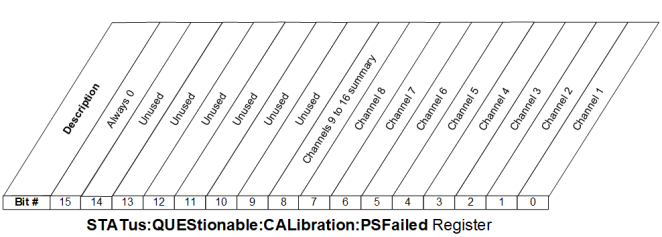

STATus:QUEStionable:CALibration:PSFailed Register

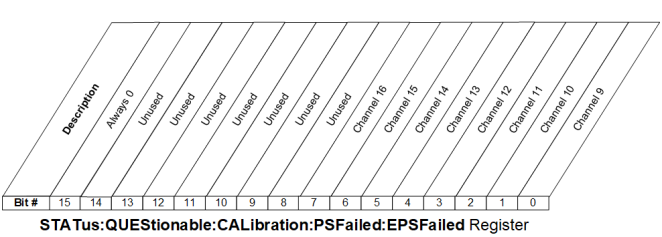

STATus:QUEStionable:CALibration:PSFailed:EPSFailed Register

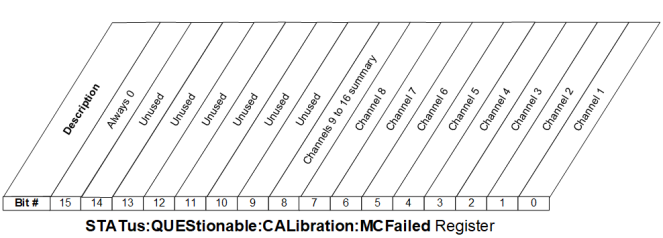

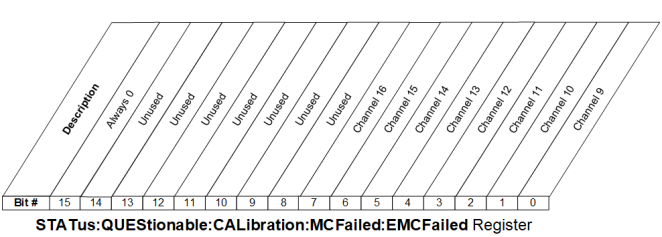

STATus:QUEStionable:CALibration:MCFailed Register

STATus:QUEStionable:CALibration:MCFailed:EMCFailed Register

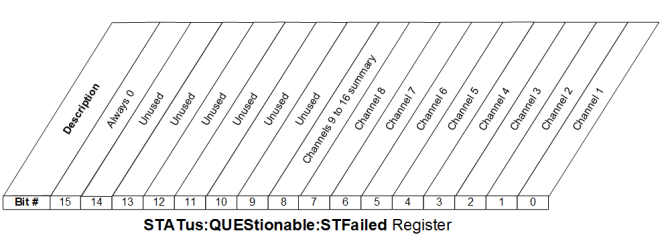

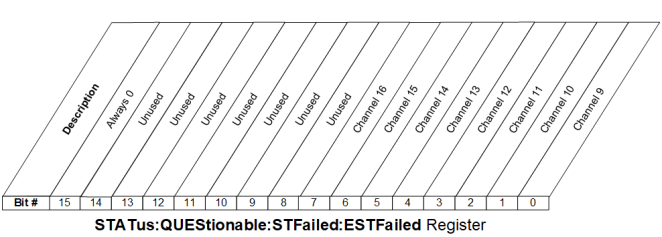

STATus:QUEStionable:STFailed Register

STATus:QUEStionable:STFailed:ESTFailed Register

The instrument supports the following subset of IEEE 488.2 Common Commands, as defined in Chapter 10 of IEEE Standard 488.2–1992. As indicated below, some of these commands correspond directly to instrument front-panel functionality, while others are available only as remote commands.

*CAL? - Calibration Query (Internal Alignments equivalent)

*RST - Reset (Mode Preset equivalent)

Performs a full alignment and returns a number indicating the success of the alignment. A zero is returned if the alignment is successful. A one is returned if any part of the alignment fails. *CAL? is the same as doing a CAL:INT? for all channels.

|

SCPI Command |

*CAL? |

|

SCPI Example |

*CAL? !Runs a full alignment and returns 0 if no problems encountered |

|

Notes |

*CAL? Will take many minutes to complete, set a timeout value on the controlling test program to a very large value. E.g. 10 minutes for a single channel instrument, 20 minutes for a dual channel instrument |

|

Initial S/W Revision |

A.01.00 |

Clears the status byte register. It does this by emptying the error queue and clearing all bits in all of the event registers, and consequently all bits in the Status Byte register.

The Status Byte register summarizes the states of the other registers. It is also responsible for generating service requests.

|

SCPI Command |

*CLS |

|

SCPI Example |

*CLS !Clears the error queue and the Status Byte Register. |

|

Notes |

For related commands, see the SYSTem:ERRor[:NEXT]? command. See also the STATus:PRESet command and all commands in the STATus subsystem. |

|

Initial S/W Revision |

A.01.00 |

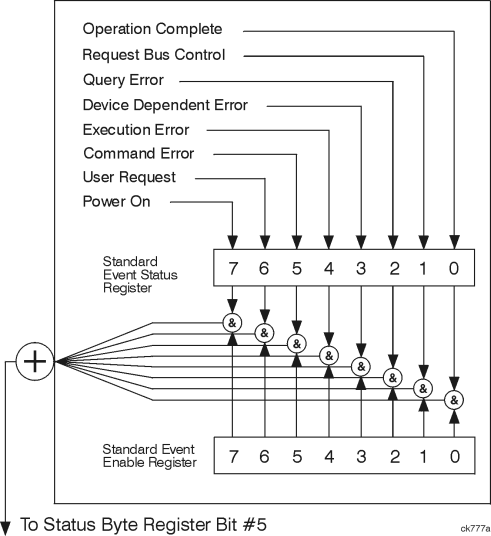

Sets the desired bits in the Event Enable Register of the Standard Event Status Register, which enables the corresponding bits in the Standard Event Status register. This register monitors I/O errors and synchronization conditions such as operation complete, request control, query error, device dependent error, status execution error, command error, and power on. The selected bits are OR’d to become a summary bit (bit 5) in the byte register which can be queried.

The query returns the state of the standard event status enable register.

Numeric values for bit patterns can be entered using decimal or hexadecimal representations (that is, 0 to 32767 is equivalent to #H0 to #H7FFF).

|

SCPI Command |

*ESE <integer> *ESE? |

|

SCPI Example |

*ESE 36 !Enables the Standard Event Status Register to monitor query and command errors (bits 2 and 5). *ESE? !Returns a 36 indicating that the query and command status bits are enabled. |

|

Notes |

For related commands, see the STATus subsystem and SYSTem:ERRor[:NEXT]? commands. |

|

State Saved |

Not saved in state. |

|

Min |

0 |

|

Max |

255 |

|

Resolution |

1 |

|

Resolution Max |

1 |

|

Initial S/W Revision |

A.01.00 |

Queries and clears the Standard Event Status Register. (This is a destructive read.) The value returned is a hexadecimal number that reflects the current state (0/1) of all the bits in the register.

|

SCPI Command |

*ESR? |

|

SCPI Example |

*ESR? !Returns a 1 if there is either a query or command error, otherwise it returns a zero. |

|

Notes |

For related commands, see the STATus subsystem commands. |

|

Preset |

0 |

|

Min |

0 |

|

Max |

255 |

|

Resolution |

1 |

|

Resolution Max |

1 |

|

Initial S/W Revision |

A.01.00 |

Returns a string of instrument identification information. The string will contain the model number, serial number, and firmware revision.

The response is organized into four fields separated by commas. The field definitions are as follows:

Manufacturer

Model

Serial number

Firmware version

|

SCPI Command |

*IDN? |

|

SCPI Example |

*IDN? !Returns instrument identification information, such as: Keysight Technologies,M9384B,US01020004,A.02.02 |

|

Initial S/W Revision |

A.01.00 |

Sets bit 0 in the standard event status register (SER) to "1" when pending operations have finished, that is when all overlapped commands are complete. It does not hold off subsequent operations. You can determine when the overlapped commands have completed either by polling the OPC bit in SER, or by setting up the status system such that a service request (SRQ) is asserted when the OPC bit is set.

The *OPC? query returns a "1" after all the current overlapped commands are complete. So it holds off subsequent commands until the "1” is returned, then the program continues. This query can be used to synchronize events of other instruments on the external bus.

|

SCPI Command |

*OPC *OPC? |

|

SCPI Example |

*OPC? !Holds off any further commands until the prior command is complete. |

|

Notes |

Not global to all remote ports or the user interface. *OPC only considers operations that were initiated on the same port as the *OPC command was issued from. *OPC is an overlapped command, but *OPC? is sequential. *OPC holds off until all overlapping commands are completed. |

|

Initial S/W Revision |

A.01.00 |

Returns a string of all the installed instrument options. It is a comma separated list, such as: 001,002,016,1E1,1EA,1EH,320,A01,D21,F11,F14,F21,F44,M04,M10,PCH,PM1,ST6,UNQ,UNT,UNZ

For the M9383B/M9384B all instrument options are listed in the response.

For theM9484C, *OPT? contains the options for channel 1 and options that pertain to the instrument regardless of how many channels are present. With the M9484C, if there are more than 1 channel present the last entry in the list will be ‘…’ which is a sentinel to indicate :SYSTem:RF<channel>:OPT? is used to query the options for channels 2 through the total number of channels.

|

SCPI Command |

*OPT? |

|

Initial S/W Revision |

A.01.00 |

For instruments with more than one RF channel, this query is used to retrieve the options that are specific for each channel.

For M9484C, *OPT? contains the instrument options that are one per instrument, and the options for channel 1. Querying channel 1 using this command will provide the options that are specific to channel 1 and not the options that are one per instrument.

For M9383B/M9384B, *OPT? contains the instrument options for the entire instrument. Querying channel 1 or channel 2 using this command will provide the options that are specific to the indicated channel.

|

SCPI Command |

:SYSTem:RF<channel>:OPT? |

|

Notes |

If the indicated <channel> doesn’t exist on the instrument an empty string is returned; e.g. “” |

|

Initial S/W Revision |

A.09.00 |

|

Modified S/W Revision |

A.11.00 Added M9383B and M9384B |

Remote command only

The default response of the *OPT? query are the options that pertain to the M9383B/M9384B in use. This command is provided to enable the *OPT? response to emulate the options of another instrument. This command can be used if you are reusing test software written for another instrument which expects a specific *OPT? response. Caution should be used emulating options of another instrument to ensure the M9383B/M9384B in use meets the RF performance of the testing scenario.

The instrument options displayed on the System Information screen are unaffected by any custom setting of *OPT?; the System Information screen always displays the options of the M9383B/M9384B.

When the instrument is power cycled, or the instrument application is restarted, the custom setting of *OPT? is restored to the options of the M9383B/M9384B. Invoking a Restore System Settings to Default Values also restores the *OPT? response to the options of the M9383B/M9384B.

The <string> parameter is a comma separated list of 3-character option identifiers. The shortest <string> accepted is 3 characters, the longest is 255 characters.

There is no validation that the M9383B/M9384B instrument in use is compatible with the emulated options set with this command. Meaning, no error will be generated if the instrument’s configuration is unsuitable for the emulated option.

Setting an empty <string> restores the *OPT? response to the M9383B/M9384B options.

|

SCPI Command |

:SYSTEM:OPT <string> |

|

SCPI Example |

SYST:OPT “506,UNY” ! Set the *OPT? response to “506,UNY” |

|

Preset |

*OPT? response is unaffected by Preset, it is set to the M9383B/M9384B options on a “Restore System Settings to Default Values” |

|

Initial S/W Revision |

A.04.00 |

Equivalent to :SYST:PRES, which is a basic Preset function. It restores all variables to a Preset state except for Persistent variables. It Includes all signals and all RF Outputs.

*RST clears all pending OPC bits.

|

SCPI Command |

*RST |

|

SCPI Example |

*RST |

|

Notes |

Sequential |

|

Annunciation |

None |

|

Annotation |

None |

|

Initial S/W Revision |

A.01.00 |

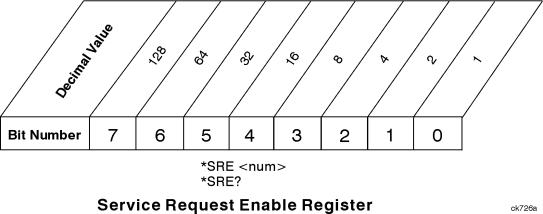

Enables the desired bits of the Service Request Enable Register.

The query returns the value of the register, indicating which bits are currently enabled.

Numeric values for bit patterns can be entered using decimal or hexadecimal representations. (that is,. 0 to 32767 is equivalent to #H0 to #H7FFF).

|

SCPI Command |

*SRE <integer> *SRE? |

|

SCPI Example |

*SRE 22 !Enables bits 1, 2, and 4 in the service request enable register. |

|

Notes |

For related commands, see the STATus subsystem and SYSTem:ERRor[:NEXT]? commands. |

|

Min |

0 |

|

Max |

255 |

|

Resolution |

1 |

|

Resolution Max |

1 |

|

Initial S/W Revision |

A.01.00 |

Returns the value of the Status Byte Register without erasing its contents.

|

SCPI Command |

*STB? |

|

SCPI Example |

*STB? !Returns a decimal value for the bits in the status byte register. !For example, if a 16 is returned, it indicates that bit 5 is set and one of the conditions monitored in the standard event status register is set. |

|

Notes |

See related command *CLS. |

|

Initial S/W Revision |

A.01.00 |

Triggers the instrument.

|

Control Path |

No equivalent key. |

|

SCPI Command |

*TRG |

|

SCPI Example |

*TRG !Triggers any number of things to happen, such as starting waveform playback, depending on the current instrument settings. |

|

Initial S/W Revision |

A.01.00 |

This query performs the internal self-test routines for all RF channels and returns a number indicating the overall success of the testing. A zero is returned if the test is successful, 1 if it fails.

|

SCPI Command |

*TST? |

|

SCPI Example |

*TST? !Runs the self-test routines and returns 0=passed, 1=some part failed. |

|

Notes |

*TST? will take many minutes to complete, set the timeout value on the controlling test program to a very large value. For example, 10 minutes for a single channel instrument, 20 minutes for a dual channel instrument. Successful completion of self-test on the channel will clear all the bits in the STATus:QUEStionable:STFailed and STATus:QUEStionable:STFailed:ESTFailed registers. Unsuccessful completion of self-test will set the applicable bit(s) in the STATus:QUEStionable:STFailed and STATus:QUEStionable:STFailed:ESTFailed registers. |

|

Initial S/W Revision |

A.01.00 |

|

Modified S/W Revision |

A.11.00 Updated with information on status bits. |

Causes the instrument to wait until all overlapped commands are completed before executing any additional commands. There is no query form for the command.

|

SCPI Command |

*WAI |

|

SCPI Example |

*WAI ! waits for completion of any prior commands. |

|

Initial S/W Revision |

A.01.00 |

The SCPI STATus Subsystem allows you to monitor a number of status conditions within the instrument through the use of a hierarchy of status registers containing bits which go true or false depending on various conditions.

This section provides an overview of SCPI status registers and how to manage them. Section STATus Subsystem Registers and Commands provides detailed programming information for each of the status registers.

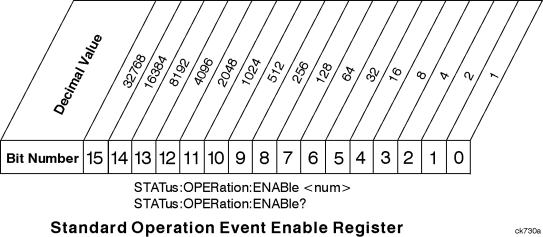

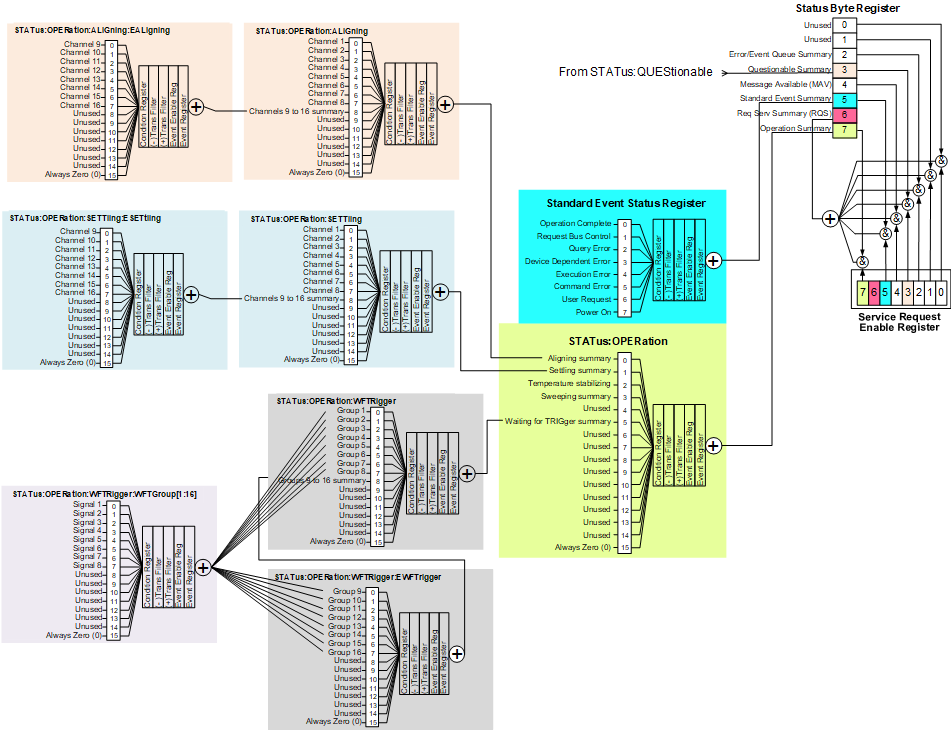

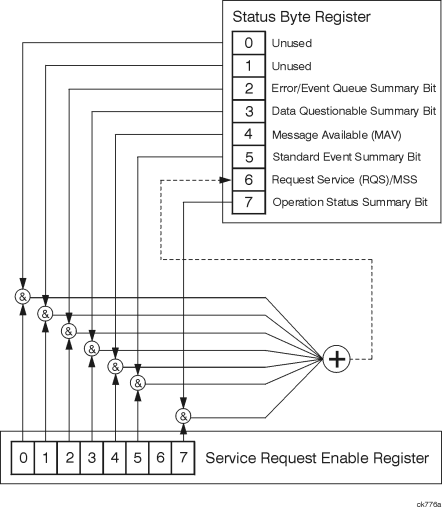

The status system contains multiple registers that are arranged in a hierarchical order. The lower-level status registers propagate their data to the higher-level registers in the data structures by means of summary bits. The status byte register is at the top of the hierarchy and contains general status information for the instrument’s events and conditions. All other individual registers are used to determine the specific events or conditions. For a diagram of the registers and their interconnections, see above.

The operation and questionable status registers are sets of registers that monitor the overall instrument condition. They are accessed with the STATus:OPERation and STATus:QUEStionable commands in the STATus command subsystem. Each register set is made up of five registers:

Condition Register—Reports the real-time state of the signals monitored by this register set. There is no latching or buffering for a condition register.

Positive Transition Register—Controls which signals will set a bit in the event register when the signal makes a low to high transition (when the condition bit changes from 0 to 1).

Negative Transition Register—Controls which signals will set a bit in the event register when the signal makes a high to low transition (when the condition bit changes from 1 to 0).

Event Register—Latches any signal state changes, in the way specified by the filter registers. Bits in the event register are never cleared by signal state changes. Event registers are cleared when read. They are also cleared by *CLS and by presetting the instrument.

Event Enable Register—Controls which of the bits, being set in the event register and will be summarized as a single output for the register set. Summary bits are then used by the next higher register.

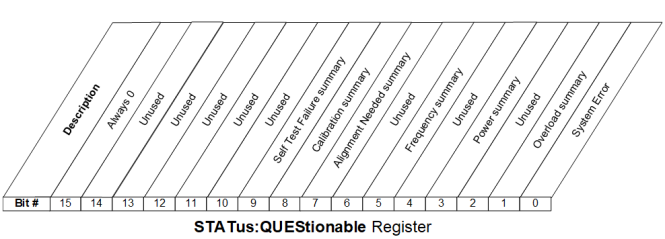

The STATus:QUEStionable registers report abnormal operating conditions. The status register hierarchy is:

The summary outputs from the six STATus:QUEStionable:<keyword> detail registers are inputs to the STATus:QUEStionable register.

The summary output from the STATus:QUEStionable register is an input to the Status Byte Register. See the overall system in the figure at the beginning of this section.

The STATus:OPERation register set has no summarized inputs. The inputs to the STATus:OPERation:CONDition register indicate the real time state of the instrument. The STATus:OPERation:EVENt register summary output is an input to the Status Byte Register.

Monitoring of the instrument conditions is done at the highest level using the following IEEE 488.2 common commands. Complete command descriptions are available in section IEEE Command Descriptions. Individual status registers can be set and queried using the commands in the STATus Subsystem Registers and Commands section.

*CLS (clear status) clears the status byte by emptying the error queue and clearing all the event registers.

*ESE, *ESE? (event status enable) sets and queries the bits in the enable register part of the standard event status register.

*ESR? (event status register) queries and clears the event register part of the standard event status register.

*OPC, *OPC? (operation complete) sets the standard event status register to monitor the completion of all commands. The query stops any new commands from being processed until the current processing is complete, then returns a ‘1’.

*PSC, *PSC? (power-on state clear) sets the power-on state so that it clears the service request enable register and the event status enable register at power on.

*SRE, *SRE? (service request enable) sets and queries the value of the service request enable register.

*STB? (status byte) queries the value of the status byte register without erasing its contents.

A program often needs to be able to detect and manage error conditions or changes in instrument status. There are two methods you can use to programmatically access the information in status registers:

The polling method

The service request (SRQ) method

In the polling method, the instrument has a passive role. It only tells the controller that conditions have changed when the controller asks the right question. In the SRQ method, the instrument takes a more active role. It tells the controller when there has been a condition change without the controller asking. Either method allows you to monitor one or more conditions.

The polling method works well if you do not need to know about changes the moment they occur. The SRQ method should be used if you must know immediately when a condition changes. To detect a change using the polling method, the program must repeatedly read the registers.

Use the SRQ method when:

you need time-critical notification of changes

you are monitoring more than one device which supports SRQs

you need to have the controller do something else while waiting

you cannot afford the performance penalty inherent to polling

Use polling when:

your programming language/development environment does not support SRQ interrupts

you want to write a simple, single-purpose program and do not want the added complexity of setting up an SRQ handler

To monitor a condition:

Determine which register contains the bit that reports the condition.

Send the unique SCPI query that reads that register.

Examine the bit to see if the condition has changed.

You can monitor conditions in different ways.

Check the current instrument hardware and firmware status. Do this by querying the condition registers which continuously monitor status. These registers represent the current state of the instrument. Bits in a condition register are updated in real time. When the condition monitored by a particular bit becomes true, the bit is set to 1. When the condition becomes false, the bit is reset to 0.

Monitor a particular condition (bit). You can enable a particular bit(s), using the event enable register. The instrument will then monitor that particular condition(s). If the bit becomes true (0 to 1 transition) in the event register, it will stay set until the event register is cleared. Querying the event register allows you to detect that this condition occurred even if the condition no longer exists. The event register can only be cleared by querying it or sending the *CLS command.

Monitor a particular type of change in a condition (bit).

The transition registers are preset to register if the condition goes from 0 to 1 (false to true, or a positive transition).

This can be changed so the selected condition is detected if the bit goes from 1 to 0 (true to false, or a negative transition).

It can also be set for both types of transitions occurring.

Or it can be set for neither transition. If both transition registers are set to 0 for a particular bit position, that bit will not be set in the event register for either type of change.

Your language, bus, and programming environment must be able to support SRQ interrupts. (For example, BASIC used with VXI-11.3 (GPIB over LAN). When you monitor a condition with the SRQ method, you must:

Determine which bit monitors the condition.

Determine how that bit reports to the request service (RQS) bit of the status byte.

Send SCPI commands to enable the bit that monitors the condition and to enable the summary bits that report the condition to the RQS bit.

Enable the controller to respond to service requests.

When the condition changes, the instrument sets its RQS bit. The controller is informed of the change as soon as it occurs. As a result, the time the controller would otherwise have used to monitor the condition can be used to perform other tasks. Your program determines how the controller responds to the SRQ.

Bit 6 of the status byte register is the request service (RQS) bit. The *SRE command is used to configure the RQS bit to report changes in instrument status. When such a change occurs, the RQS bit is set. It is cleared when the status byte register is queried using *SRE? (with a serial poll.) It can be queried without erasing the contents with *STB?.

When a register being set causes a summary bit in the status byte to change from 0 to 1, the instrument can initiate the service request (SRQ) process. However, the process is only initiated if both of the following conditions are true:

The corresponding bit of the service request enable register is also set to 1.

The instrument does not have a service request pending. (A service request is considered to be pending between the time the instrument’s SRQ process is initiated and the time the controller reads the status byte register.)

The SRQ process sets the SRQ true. It also sets the status byte’s request service (RQS) bit to 1. Both actions are necessary to inform the controller that the instrument requires service. Setting the SRQ line only informs the controller that some device on the bus requires service. Setting the RQS bit allows the controller to determine which instrument requires service.

If your program enables the controller to detect and respond to service requests, it should instruct the controller to perform a serial poll when the SRQ is set true. Each device on the bus returns the contents of its status byte register in response to this poll. The device who's RQS bit is set to 1 is the device that requested service.

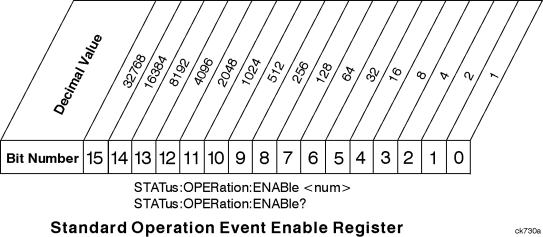

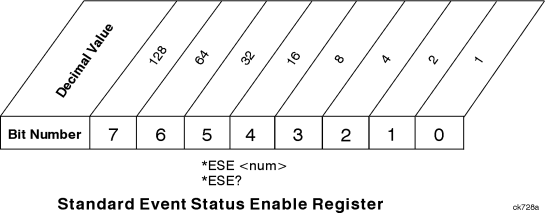

The figure below shows a typical status register, the Standard Operation Event Enable register. Each bit in a register is represented by a numerical value based on its location. This number is sent with the command to enable a particular bit. If you want to enable more than one bit, you would send the sum of all the bits that you want to monitor.

Figure: Status Register Bit Values

Example 1:

To enable bit 0 and bit 6 of standard event status register, you would send the command *ESE 65 because 1 + 64 = 65.

Example 2:

Suppose you want to know if an Auto-trigger Timeout occurs, but you only cared about that specific condition. So you would want to know what was happening with bit 10 in the Status Questionable Integrity register, and not about any other bits.

It is usually a good idea to start by clearing all the status registers with *CLS.

Sending the STAT:QUES:INT:ENAB 1024 command lets you monitor only bit 10 events, instead of the default monitoring all the bits in the register. The register default is for positive transition events (0 to 1 transition). That is, when an auto-trigger timeout occurs. If instead, you wanted to know when the Auto-trigger timeout condition is cleared, then you would set the STAT:QUES:INT:PTR 0 and the STAT:QUES:INT:NTR 32767.

So now the only output from the Status Questionable Integrity register will come from a bit 10 positive transition. That output goes to the Integrity Sum bit 9 of the Status Questionable register.

You can do a similar action with this register to only look at bit 9 using, STAT:QUES:ENAB 512.

The Status Questionable register output goes to the “Status Questionable Summary” bit 3 of the Status Byte Register. The output from this register can be enabled using the *SRE 8 command.

Finally, you would use the serial polling functionality available for the particular bus/software that you are using to monitor the Status Byte Register. (You could also use *STB? to poll the Status Byte Register.)

The STATus subsystem remote commands set and query the status registers. This system of registers monitor various events and conditions in the instrument. Software written to control the instrument may need to monitor some of these events and conditions.

Specific status bits are assigned to monitor various aspects of the instrument operation and status. See the Status Register Diagrams for information about the bit assignments and status register interconnections. See also the Instrument Messages for more detail on the instrument conditions that can cause these bits to be set.

The STATus subsystem controls and queries the SCPI-defined instrument status reporting structures. Each status register has a set of five commands used for querying or masking that particular register.

Numeric values for bit patterns can be entered using decimal or hexadecimal representations. (i.e. 0 to 32767 is equivalent to #H0 to #H7FFF. It is also equal to all ones, 111111111111111). See Status Register Bit Parameters for information about using bit patterns for variable parameters.

The following diagrams provide a graphical overview of the Status Register subsystem.

Status Register Diagram 1 of 2 (View larger image)

Status Register Diagram 2 of 2 (View larger image)

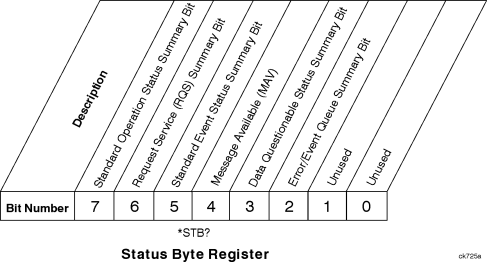

Provides a one-byte overview of the entire STATus subsystem. All other registers funnel into this register with summary bits, as shown in the Status Register Diagram.

|

Bit |

Description |

|---|---|

|

0,1 |

These bits are always set to 0. |

|

2 |

A 1 in this bit position indicates that the SCPI error queue is not empty, which means that it contains at least one error message. |

|

3 |

A 1 in this bit position indicates that the data questionable summary bit has been set. The data questionable event register can then be read to determine the specific condition that caused this bit to be set. |

|

4 |

A 1 in this bit position indicates that the instrument has data ready in the output queue. There are no lower status groups that provide input to this bit. |

|

5 |

A 1 in this bit position indicates that the standard event summary bit has been set. The standard event status register can then be read to determine the specific event that caused this bit to be set. |

|

6 |

A 1 in this bit position indicates that the instrument has at least one reason to report a status change. This bit is also called the master summary status bit (MSS). |

|

7 |

A 1 in this bit position indicates that the standard operation summary bit has been set. The standard operation event register can then be read to determine the specific condition that caused this bit to be set. |

To query the status byte register, send the command *STB? The response will be the decimal sum of the bits which are set to 1. For example, if bit number 7 and bit number 3 are set to 1, the decimal sum of the 2 bits is 128 plus 8. So the decimal value 136 is returned. The *STB command does not clear the status register.

The RQS bit is read and reset by a serial poll. The same bit position (MSS) is read, non-destructively by the *STB? command. If you serial poll bit 6 it is read as RQS, but if you send *STB it reads bit 6 as MSS. For more information refer to IEEE 488.2 standards, section 11. In addition to the status byte register, the status byte group also contains the service request enable register. This register lets you choose which bits in the status byte register will trigger a service request.

See also *STB? - Status Byte Query.

Enables the desired bits of the Service Request (SRQ) subsystem.

Send the *SRE <integer> command, where <integer> is the sum of the decimal values of the bits you want to enable plus the decimal value of bit 6. For example, assume that you want to enable bit 7 so that whenever the standard operation status register summary bit is set to 1 it will trigger a service request. Send the command *SRE 192 (because 192 = 128 + 64). You must always add 64 (the numeric value of RQS bit 6) to your numeric sum when you enable any bits for a service request.

The command *SRE? returns the decimal value of the sum of the bits previously enabled with the *SRE <integer> command.

The service request enable register presets to zeros (0).

See also *SRE - Service Request Enable .

Sets bits in most of the enable and transition registers to their default state. It presets all the Transition Filters, Enable Registers, and the Error/Event Queue Enable. It has no effect on Event Registers, Error/Event QUEue, IEEE 488.2 ESE, and SRE Registers as described in IEEE Standard 488.2-1992, IEEE Standard Codes, Formats, Protocols, and Common Commands for Use with ANSI/IEEE Std 488.1-1987. New York, NY, 1992.

|

SCPI Command |

:STATus:PRESet |

|

SCPI Example |

STAT:PRES |

|

Initial S/W Revision |

A.01.00 |

The standard event status register contains the following bits:

|

Bit |

Description |

|---|---|

|

0 |

A 1 in this bit position indicates that all pending operations were completed following execution of the *OPC command. |

|

1 |

This bit is for GPIB handshaking to request control. Currently it is set to 0 because there are no implementations where the instrument controls another instrument. |

|

2 |

A 1 in this bit position indicates that a query error has occurred. Query errors have SCPI error numbers from -499 to -400. |

|

3 |

A 1 in this bit position indicates that a device dependent error has occurred. Device dependent errors have SCPI error numbers from -399 to -300 and 1 to 32767. |

|

4 |

A 1 in this bit position indicates that an execution error has occurred. Execution errors have SCPI error numbers from -299 to -200. |

|

5 |

A 1 in this bit position indicates that a command error has occurred. Command errors have SCPI error numbers from -199 to -100. |

|

6 |

User Request Key (Local) - reserved for future use. |

|

7 |

A 1 in this bit position indicates that the instrument has been turned off and then on. |

The standard event status register is used to determine the specific event that set bit 5 in the status byte register. To query the standard event status register, send the command *ESR?. The response will be the decimal sum of the bits which are enabled (set to 1). For example, if bit number 7 and bit number 3 are enabled, the decimal sum of the 2 bits is 128 plus 8. So the decimal value 136 is returned. See also the *ESR? - Standard Event Status Register Query .

In addition to the standard event status register, the standard event status group also contains a standard event status enable register. This register lets you choose which bits in the standard event status register will set the summary bit (bit 5 of the status byte register) to 1. Send the *ESE <integer> command where <integer> is the sum of the decimal values of the bits you want to enable. For example, to enable bit 7 and bit 6 so that whenever either of those bits is set to 1, the standard event status summary bit of the status byte register will be set to 1, send the command *ESE 192 (128 + 64). The command *ESE? returns the decimal value of the sum of the bits previously enabled with the *ESE <integer> command.

The standard event status enable register presets to zeros (0).

See also *ESE - Standard Event Status Enable .

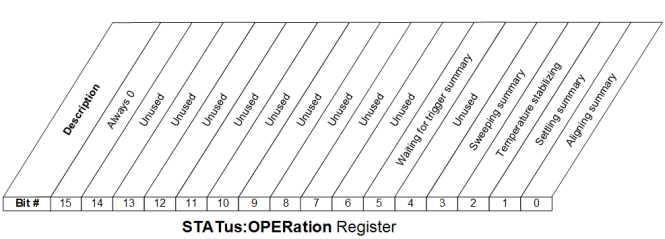

The operation and questionable status registers monitor the overall instrument condition. They are accessed with the STATus:OPERation and STATus:QUEStionable commands.

The operation status register monitors the current instrument state and various instrument operations for a quick summary of what is happening within the instrument. It checks to see if the instrument is calibrating, sweeping, or waiting for a trigger. See also *OPC? - Operation Complete .

|

Bit |

Condition |

Operation |

|---|---|---|

|

0 |

Aligning summary |

The instrument is busy aligning on any channel. |

|

1 |

Settling summary |

The instrument circuitry is settling on any channel. |

|

2 |

Temperature stabilizing |

The instrument is warming up, or the environment is changing |

|

3 |

Sweeping summary |

Reserved for future. |

|

4 |

Unused |

|

|

5 |

Waiting for trigger summary |

The instrument is waiting for the trigger conditions to be met, then it will trigger a sweep, or initiate vector modulation, on any group. |

Returns the decimal value of the sum of the bits in the Status Operation Condition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:CONDition? |

|

SCPI Example |

STAT:OPER:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Initial S/W Revision |

A.01.00 |

Returns the value of the indicated bit in the Status Operation Condition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:BIT{0:15}:CONDition? |

|

SCPI Example |

STAT:OPER:BIT5:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Initial S/W Revision |

A.01.00 |

Determines which bits in the Operation Event register, will set the Operation Status Summary bit (bit 7) in the Status Byte Register. The variable <integer> is the sum of the decimal values of the bits you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ENABle <integer> :STATus:OPERation:ENABle? |

|

SCPI Example |

STAT:OPER:ENAB 1 !Sets the register so that I/Q Calibrating events will be reported to the Status Byte Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Initial S/W Revision |

A.01.00 |

Permits setting or querying an individual bit in the Operation Status register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:BIT{0:15}:ENABle 0|1 :STATus:OPERation:BIT{0:15}:ENABle? |

|

SCPI Example |

STAT:OPER:BIT0:ENAB 1 !Sets the register so that I/Q Calibrating events will be reported to the Status Byte Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

1 |

|

Initial S/W Revision |

A.01.00 |

Returns the decimal value of the sum of the bits in the Operation Event register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation[:EVENt]? |

|

SCPI Example |

STAT:OPER? |

|

Preset |

STATus:PREset resets to 0 |

|

Initial S/W Revision |

A.01.00 |

Returns the indicated bit in the Operation Event register

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:BIT{0:15}[:EVENt]? |

|

SCPI Example |

STAT:OPER:BIT5? |

|

Preset |

STATus:PREset resets to 0 |

|

Initial S/W Revision |

A.01.00 |

Determines which bits in the Operation Condition register will set the corresponding bit in the Operation Event register, when the condition register bit has a negative transition (1 to 0). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:NTRansition <integer> :STATus:OPERation:NTRansition? |

|

SCPI Example |

STAT:OPER:NTR 1 ! I/Q Calibrating operation complete will be reported to the Status Byte Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Initial S/W Revision |

A.01.00 |

Provides individual bit access to the Operation Condition Negative Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:BIT{0:15}:NTRansition 0|1 :STATus:OPERation:BIT{0:15}:NTRansition? |

|

SCPI Example |

STAT:OPER:BIT0:NTR 1 ! I/Q Calibrating operation complete will be reported to the Status Byte Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

1 |

|

Initial S/W Revision |

A.01.00 |

Determines which bits in the Operation Condition register will set the corresponding bit in the Operation Event register, when the condition register bit has a positive transition (0 to 1). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:PTRansition <integer> :STATus:OPERation:PTRansition? |

|

SCPI Example |

STAT:OPER:PTR 1 ! I/Q Calibrating operation beginning will be reported to the Status Byte Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Initial S/W Revision |

A.01.00 |

Provides individual bit access to the Operation Condition Positive Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:BIT{0:15}:PTRansition 0|1 :STATus:OPERation:BIT{0:15}:PTRansition? |

|

SCPI Example |

STAT:OPER:BIT0:PTR 1 ! I/Q Calibrating operation complete will be reported to the Status Byte Register. |

|

Preset |

STATus:PREset resets to 1 |

|

Min |

0 |

|

Max |

1 |

|

Initial S/W Revision |

A.01.00 |

The operation ALIGning register indicates the channels that have raised an alignment in progress condition.

|

Bit |

Condition |

Operation |

|---|---|---|

|

0 |

Channel 1 |

Alignment in progress on channel 1 |

|

1 |

Channel 2 |

Alignment in progress on channel 2 |

|

2 |

Channel 3 |

Alignment in progress on channel 3 |

|

3 |

Channel 4 |

Alignment in progress on channel 4 |

|

4 |

Channel 5 |

Alignment in progress on channel 5 |

|

5 |

Channel 6 |

Alignment in progress on channel 6 |

|

6 |

Channel 7 |

Alignment in progress on channel 7 |

|

7 |

Channel 8 |

Alignment in progress on channel 8 |

|

8 |

Channels 9 to 16 summary |

One of the channels from 9 to 16 have raised an alignment in progress condition, an entry in STATus:OPERation:ALIGning:EALigning register is set. |

This query returns the decimal value of the sum of the bits in the Operation ALIGning Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:CONDition? |

|

SCPI Example |

:STAT:OPER:ALIG:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the value of the indicated bit in the Operation ALIGning Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning: BIT{0:15}:CONDition? |

|

SCPI Example |

:STAT:OPER:ALIG:BIT1:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation ALIGning Event register will set the Aligning Summary bit (bit 0) in the Status Operation Register. The variable <integer> is the sum of the decimal values of the bits you want to enable.

The preset condition is all bits in this enable register set to 1, delivering any event in the Operation ALIGning Event register to the Aligning Summary bit. The Status Operation Event Register should be queried to check the instrument is finished aligning (bit 0).

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:ENABle <integer> :STATus:OPERation:ALIGning:ENABle? |

|

SCPI Example |

:STAT:OPER:ALIG:ENAB 2 !Sets the register so that alignment in progress events on Channel 2 will be reported to the Status Operation Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command permits setting or querying and individual bit in the Operation ALIGning Enable register

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:BIT{0:15}:ENABle 0|1 :STATus:OPERation:ALIGning:BIT{0:15}:ENABle? |

|

SCPI Example |

:STAT:OPER:ALIG:BIT1:ENAB 1 !Sets the register so that alignment in progress events on Channel 2 will be reported to the Status Operation Register. |

|

Preset |

STATus:PREset resets to 1 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the decimal value of the sum of the bits in the Operation ALIGning Event register.

The register requires that the associated PTR or NTR filters be set before a condition register bit can set a bit in the event register. The data in this register is latched until it is queried. Once queried, the register is cleared.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning[:EVENt]? |

|

SCPI Example |

:STAT:OPER:ALIG? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the value of the indicated bit in the Operation ALIGning Event register.

The register requires that the associated PTR or NTR filters be set before a condition register bit can set a bit in the event register. The data in this register is latched until it is queried. Once queried, the register is cleared.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:BIT{0:15}[:EVENt]? |

|

SCPI Example |

:STAT:OPER:ALIG:BIT1? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation ALIGning Condition register will set the corresponding bit in the Operation ALIGning Event register when the condition register bit has a negative transition (1 to 0). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:NTRansition <integer> :STATus:OPERation:ALIGning:NTRansition? |

|

SCPI Example |

:STAT:OPER:ALIG:NTR 2 ! Alignment in progress ‘operation cleared’ on Channel 2 will be reported to the Status Operation ALIGning Event Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command provides individual bit access to the Operation ALIGning Condition Negative Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:BIT{0:15}:NTRansition 0|1 :STATus:OPERation:ALIGning:BIT{0:15}:NTRansition? |

|

SCPI Example |

:STAT:OPER:ALIG:BIT1:NTR 1 ! Alignment in progress ‘operation cleared’ on Channel 2 will be reported to the Status Operation ALIGning Event Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation ALIGning Condition register will set the corresponding bit in the Operation ALIGning Event register when the condition register bit has a positive transition (0 to 1). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:PTRansition <integer> :STATus:OPERation:ALIGning:PTRansition? |

|

SCPI Example |

:STAT:OPER:ALIG:PTR 2 ! Alignment in progress ‘operation asserted’ on Channel 2 will be reported to the Status Operation ALIGning Event Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command provides individual bit access to the Operation ALIGning Condition Positive Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:BIT{0:15}:PTRansition 0|1 :STATus:OPERation:ALIGning:BIT{0:15}:PTRansition? |

|

SCPI Example |

:STAT:OPER:ALIG:BIT1:PTR 1 ! Alignment in progress ‘operation asserted’ on Channel 2 will be reported to the Status Operation ALIGning Event Register. |

|

Preset |

STATus:PREset resets to 1 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

The operation ALIGning EALigning (Extended Aligning) register indicates if channels 9 through 16 have raised an alignment in progress condition.

|

Bit |

Condition |

Operation |

|---|---|---|

|

0 |

Channel 9 |

Alignment in progress on channel 9 |

|

1 |

Channel 10 |

Alignment in progress on channel 10 |

|

2 |

Channel 11 |

Alignment in progress on channel 11 |

|

3 |

Channel 12 |

Alignment in progress on channel 12 |

|

4 |

Channel 13 |

Alignment in progress on channel 13 |

|

5 |

Channel 14 |

Alignment in progress on channel 14 |

|

6 |

Channel 15 |

Alignment in progress on channel 15 |

|

7 |

Channel 16 |

Alignment in progress on channel 16 |

This query returns the decimal value of the sum of the bits in the Operation ALIGning EALigning Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning:CONDition? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the value of the indicated bit in the Operation ALIGning EALigning Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning:BIT{0:15}:CONDition? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL:BIT1:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation ALIGning EALigning Event register will set the Channels 9 to 16 Summary bit (bit8) in the Status Operation ALIGning Register. The variable <integer> is the sum of the decimal values of the bits you want to enable.

The preset condition is all bits in this enable register set to 1, delivering any event in the Operation ALIGning EALigning Event register to the Channels 9 to 16 Summary bit.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning:ENABle <integer> :STATus:OPERation:ALIGning:EALigning:ENABle? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL:ENAB 2 !Sets the register so that alignment in progress events on Channel 10 will be reported to the Status Operation ALIGning Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command permits setting or querying and individual bit in the Operation ALIGning EALigning Enable register

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning:BIT{0:15}:ENABle 0|1 :STATus:OPERation:ALIGning:EALigning:BIT{0:15}:ENABle? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL:BIT1:ENAB 1 !Sets the register so that alignment in progress events on Channel 10 will be reported to the Status Operation ALIGning Register. |

|

Preset |

STATus:PREset resets to 1 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the decimal value of the sum of the bits in the Operation ALIGning EALigning Event register.

The register requires that the associated PTR or NTR filters be set before a condition register bit can set a bit in the event register. The data in this register is latched until it is queried. Once queried, the register is cleared.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning[:EVENt]? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the value of the indicated bit in the Operation ALIGning EALigning Event register.

The register requires that the associated PTR or NTR filters be set before a condition register bit can set a bit in the event register. The data in this register is latched until it is queried. Once queried, the register is cleared.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning:BIT{0:15}[:EVENt]? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL:BIT1? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation ALIGning EALigning Condition register will set the corresponding bit in the Operation ALIGning EALigning Event register when the condition register bit has a negative transition (1 to 0). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning:NTRansition <integer> :STATus:OPERation:ALIGning:EALigning:NTRansition? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL:NTR 2 ! Alignment in progress ‘operation cleared’ on Channel 10 will be reported to the Status Operation ALIGning EALigning Event Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command provides individual bit access to the Operation ALIGning EALigning Condition Negative Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning:BIT{0:15}:NTRansition 0|1 :STATus:OPERation:ALIGning:EALigning:BIT{0:15}:NTRansition? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL:BIT1:NTR 1 ! Alignment in progress ‘operation cleared’ on Channel 10 will be reported to the Status Operation ALIGning EALigning Event Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation ALIGning EALigning Condition register will set the corresponding bit in the Operation ALIGning EALigning Event register when the condition register bit has a positive transition (0 to 1). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning:PTRansition <integer> :STATus:OPERation:ALIGning:EALigning:PTRansition? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL:PTR 2 ! Alignment in progress ‘operation asserted’ on Channel 10 will be reported to the Status Operation ALIGning EALigning Event Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command provides individual bit access to the Operation ALIGning EALigning Condition Positive Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:ALIGning:EALigning:BIT{0:15}:PTRansition 0|1 :STATus:OPERation:ALIGning:EALigning:BIT{0:15}:PTRansition? |

|

SCPI Example |

:STAT:OPER:ALIG:EAL:BIT1:PTR 1 ! Alignment in progress ‘operation asserted’ on Channel 10 will be reported to the Status Operation ALIGning EALigning Event Register. |

|

Preset |

STATus:PREset resets to 1 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

The operation SETTling register indicates the channels that have raised a circuitry is settling condition.

|

Bit |

Condition |

Operation |

|---|---|---|

|

0 |

Channel 1 |

Circuitry is settling on channel 1 |

|

1 |

Channel 2 |

Circuitry is settling on channel 2 |

|

2 |

Channel 3 |

Circuitry is settling on channel 3 |

|

3 |

Channel 4 |

Circuitry is settling on channel 4 |

|

4 |

Channel 5 |

Circuitry is settling on channel 5 |

|

5 |

Channel 6 |

Circuitry is settling on channel 6 |

|

6 |

Channel 7 |

Circuitry is settling on channel 7 |

|

7 |

Channel 8 |

Circuitry is settling on channel 8 |

|

8 |

Channels 9 to 16 summary |

One of the channels from 9 to 16 have raised a circuitry is settling condition, an entry in STATus:OPERation:SETTling:ESETtling register is set. |

This query returns the decimal value of the sum of the bits in the Operation SETTling Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:CONDition? |

|

SCPI Example |

:STAT:OPER:SETT:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the value of the indicated bit in the Operation SETTling Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:BIT{0:15}:CONDition? |

|

SCPI Example |

:STAT:OPER:SETT:BIT1:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation SETTling Event register will set the Settling Summary bit (bit1) in the Status Operation Register. The variable <integer> is the sum of the decimal values of the bits you want to enable.

The preset condition is all bits in this enable register set to 1, delivering any event in the Operation SETTling Event register to the Settling Summary bit. The Status Operation Event Register should be queried to check the instrument is settled (bit 1).

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ENABle <integer> :STATus:OPERation:SETTling:ENABle? |

|

SCPI Example |

:STAT:OPER:SETT:ENAB 2 !Sets the register so that circuitry is settling events on Channel 2 will be reported to the Status Operation Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command permits setting or querying and individual bit in the Operation SETTling Enable register

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:BIT{0:15}:ENABle 0|1 :STATus:OPERation:SETTling:BIT{0:15}:ENABle? |

|

SCPI Example |

:STAT:OPER:SETT:BIT1:ENAB 1 !Sets the register so that circuitry is settling events on Channel 2 will be reported to the Status Operation Register. |

|

Preset |

STATus:PREset resets to 1 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the decimal value of the sum of the bits in the Operation SETTling Event register.

The register requires that the associated PTR or NTR filters be set before a condition register bit can set a bit in the event register. The data in this register is latched until it is queried. Once queried, the register is cleared.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling[:EVENt]? |

|

SCPI Example |

:STAT:OPER:SETT? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the value of the indicated bit in the Operation SETTling Event register.

The register requires that the associated PTR or NTR filters be set before a condition register bit can set a bit in the event register. The data in this register is latched until it is queried. Once queried, the register is cleared.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:BIT{0:15}[:EVENt]? |

|

SCPI Example |

:STAT:OPER:SETT:BIT1? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation SETTling Condition register will set the corresponding bit in the Operation SETTling Event register when the condition register bit has a negative transition (1 to 0). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:NTRansition <integer> :STATus:OPERation:SETTling:NTRansition? |

|

SCPI Example |

:STAT:OPER:SETT:NTR 2 ! Circuitry is settling ‘operation cleared’ on Channel 2 will be reported to the Status Operation SETTling Event Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command provides individual bit access to the Operation SETTling Condition Negative Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:BIT{0:15}:NTRansition 0|1 :STATus:OPERation:SETTling:BIT{0:15}:NTRansition? |

|

SCPI Example |

:STAT:OPER:SETT:BIT1:NTR 1 ! Circuitry is settling ‘operation cleared’ on Channel 2 will be reported to the Status Operation SETTling Event Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation SETTling Condition register will set the corresponding bit in the Operation SETTling Event register when the condition register bit has a positive transition (0 to 1). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:PTRansition <integer> :STATus:OPERation:SETTling:PTRansition? |

|

SCPI Example |

:STAT:OPER:SETT:PTR 2 ! Circuitry is settling ‘operation asserted’ on Channel 2 will be reported to the Status Operation SETTling Event Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command provides individual bit access to the Operation SETTling Condition Positive Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:BIT{0:15}:PTRansition 0|1 :STATus:OPERation:SETTling:BIT{0:15}:PTRansition? |

|

SCPI Example |

:STAT:OPER:SETT:BIT1:PTR 1 ! Circuitry is settling ‘operation asserted’ on Channel 2 will be reported to the Status Operation SETTling Event Register. |

|

Preset |

STATus:PREset resets to 1 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

The operation SETTling ESETtling (Extended Settling) register indicates if channels 9 through 16 have raised a circuitry is settling condition.

|

Bit |

Condition |

Operation |

|---|---|---|

|

0 |

Channel 9 |

Circuitry is settling on channel 9 |

|

1 |

Channel 10 |

Circuitry is settling on channel 10 |

|

2 |

Channel 11 |

Circuitry is settling on channel 11 |

|

3 |

Channel 12 |

Circuitry is settling on channel 12 |

|

4 |

Channel 13 |

Circuitry is settling on channel 13 |

|

5 |

Channel 14 |

Circuitry is settling on channel 14 |

|

6 |

Channel 15 |

Circuitry is settling on channel 15 |

|

7 |

Channel 16 |

Circuitry is settling on channel 16 |

This query returns the decimal value of the sum of the bits in the Operation SETTling ESETtling Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling:CONDition? |

|

SCPI Example |

:STAT:OPER:SETT:ESET:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the value of the indicated bit in the Operation SETTling ESETtling Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling:BIT{0:15}:CONDition? |

|

SCPI Example |

:STAT:OPER:SETT:ESET:BIT1:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation SETTling ESETtling Event register will set the Channels 9 to 16 Summary bit (bit8) in the Status Operation SETTling Register. The variable <integer> is the sum of the decimal values of the bits you want to enable.

The preset condition is all bits in this enable register set to 1, delivering any event in the Operation SETTling ESETtling Event register to the Channels 9 to 16 Summary bit.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling:ENABle <integer> :STATus:OPERation:SETTling:ESETtling:ENABle? |

|

SCPI Example |

:STAT:OPER:SETT:ESET:ENAB 2 !Sets the register so that circuitry is settling events on Channel 10 will be reported to the Status Operation SETTling Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command permits setting or querying and individual bit in the Operation SETTling ESETtling Enable register

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling:BIT{0:15}:ENABle 0|1 :STATus:OPERation:SETTling:ESETtling:BIT{0:15}:ENABle? |

|

SCPI Example |

:STAT:OPER:SETT:ESET:BIT1:ENAB 1 !Sets the register so that circuitry is settling events on Channel 10 will be reported to the Status Operation SETTling Register. |

|

Preset |

STATus:PREset resets to 1 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the decimal value of the sum of the bits in the Operation SETTling ESETtling Event register.

The register requires that the associated PTR or NTR filters be set before a condition register bit can set a bit in the event register. The data in this register is latched until it is queried. Once queried, the register is cleared.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling[:EVENt]? |

|

SCPI Example |

:STAT:OPER:SETT:ESET? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the value of the indicated bit in the Operation SETTling ESETtling Event register.

The register requires that the associated PTR or NTR filters be set before a condition register bit can set a bit in the event register. The data in this register is latched until it is queried. Once queried, the register is cleared.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling:BIT{0:15}[:EVENt]? |

|

SCPI Example |

:STAT:OPER:SETT:ESET:BIT1? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation SETTling ESETtling Condition register will set the corresponding bit in the Operation SETTling ESETtling Event register when the condition register bit has a negative transition (1 to 0). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling:NTRansition <integer> :STATus:OPERation:SETTling:ESETtling:NTRansition? |

|

SCPI Example |

:STAT:OPER:SETT:ESET:NTR 2 ! Circuitry is settling ‘operation cleared’ on Channel 10 will be reported to the Status Operation SETTling ESETtling Event Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command provides individual bit access to the Operation SETTling ESETtling Condition Negative Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling:BIT{0:15}:NTRansition 0|1 :STATus:OPERation:SETTling:ESETtling:BIT{0:15}:NTRansition? |

|

SCPI Example |

:STAT:OPER:SETT:ESET:BIT1:NTR 1 ! Circuitry is settling ‘operation cleared’ on Channel 10 will be reported to the Status Operation SETTling ESETtling Event Register. |

|

Preset |

STATus:PREset resets to 0 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation SETTling ESETtling Condition register will set the corresponding bit in the Operation SETTling ESETtling Event register when the condition register bit has a positive transition (0 to 1). The variable <integer> is the sum of the decimal values of the bits that you want to enable.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling:PTRansition <integer> :STATus:OPERation:SETTling:ESETtling:PTRansition? |

|

SCPI Example |

:STAT:OPER:SETT:ESET:PTR 2 ! Circuitry is settling ‘operation asserted’ on Channel 10 will be reported to the Status Operation SETTling ESETtling Event Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command provides individual bit access to the Operation SETTling ESETtling Condition Positive Transition register.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:SETTling:ESETtling:BIT{0:15}:PTRansition 0|1 :STATus:OPERation:SETTling:ESETtling:BIT{0:15}:PTRansition? |

|

SCPI Example |

:STAT:OPER:SETT:ESET:BIT1:PTR 1 ! Circuitry is settling ‘operation asserted’ on Channel 10 will be reported to the Status Operation SETTling ESETtling Event Register. |

|

Preset |

STATus:PREset resets to 1 |

|

Min |

0 |

|

Max |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

The operation WFTRigger register indicates the groups that have raised a waiting for trigger condition.

|

Bit |

Condition |

Operation |

|---|---|---|

|

0 |

Group 1 |

Waiting for trigger on group 1 |

|

1 |

Group 2 |

Waiting for trigger on group 2 |

|

2 |

Group 3 |

Waiting for trigger on group 3 |

|

3 |

Group 4 |

Waiting for trigger on group 4 |

|

4 |

Group 5 |

Waiting for trigger on group 5 |

|

5 |

Group 6 |

Waiting for trigger on group 6 |

|

6 |

Group 7 |

Waiting for trigger on group 7 |

|

7 |

Group 8 |

Waiting for trigger on group 8 |

|

8 |

Groups 9 to 16 summary |

One of the groups from 9 to 16 have raised a waiting for trigger condition, an entry in STATus:OPERation:WFTRigger:EWFTrigger register is set. |

This query returns the decimal value of the sum of the bits in the Operation WFTRigger Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:WFTRigger:CONDition? |

|

SCPI Example |

:STAT:OPER:WFTR:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This query returns the value of the indicated bit in the Operation WFTRigger Condition register.

The data in this register is continuously updated and reflects the current conditions.

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:WFTRigger:BIT{0:15}:CONDition? |

|

SCPI Example |

:STAT:OPER:WFTR:BIT1:COND? |

|

Preset |

STATus:PREset resets to 0 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |

This command determines which bits in the Operation WFTRigger Event register will set the Waiting For Trigger Summary bit (bit5) in the Status Operation Register. The variable <integer> is the sum of the decimal values of the bits you want to enable.

The preset condition is all bits in this enable register set to 1, delivering any event in the Operation WFTRigger Event register to the Waiting For Trigger Summary bit. The Status Operation Event Register should be queried to check the instrument is waiting for trigger (bit 5).

|

Mode |

All |

|

SCPI Command |

:STATus:OPERation:WFTRigger:ENABle <integer> :STATus:OPERation:WFTRigger:ENABle? |

|

SCPI Example |

:STAT:OPER:WFTR:ENAB 2 !Sets the register so that waiting for trigger events on Group 2 will be reported to the Status Operation Register. |

|

Preset |

STATus:PREset resets to 32767 |

|

Min |

0 |

|

Max |

32767 |

|

Resolution |

1 |

|

Status Bits/OPC dependencies |

Sequential command |

|

Initial S/W Revision |

A.11.50 |