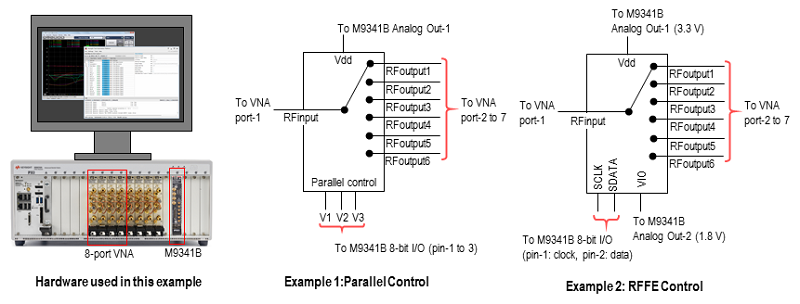

This example shows a procedure for testing a SP6T RF switch with the PXIe VNA based AMX system. The DUT mode (switch state) is controlled with the M9341B PXIe Digital and Analog I/O module. To edit the multimode DUT test plan efficiently, Microsoft Excel is used in combination with the AMX Test Plan Builder.

|

Instruments: |

M937xA PXIe VNA, M9341B PXIe Digital and Analog I/O Module |

|||||||||||||||||||||||||||||||||||

|

Test parameters |

Insertion loss & isolation between RF input and RF output ports in 6 DUT modes. |

|||||||||||||||||||||||||||||||||||

|

Calibration: |

Full 7-port calibration |

|||||||||||||||||||||||||||||||||||

|

Test specs: |

|

|||||||||||||||||||||||||||||||||||

|

DUT mode control: (Parallel Control Example) |

3-bit parallel control voltages, logic level 3.3 V (same as Vdd level)

Vdd and parallel control voltages are turned on and off before starting and after completing the DUT test sequence. |

|||||||||||||||||||||||||||||||||||

|

(RFFE Control Example) |

Vdd 3.3 V and VIO 1.8 V must be turned on and off before starting and after completing the DUT measurement. |

The AMX version must be ver.1.5 or above.

The M9341A/B I/O Module Driver must be installed on the PXIe controller. The AMX controls the M9341B directly, not through VNA.

The VNA firmware version must be A.12.55.05 or above.

|

VNA |

DUT |

|

Port 1 |

RF Input 1 |

|

Port 2 |

RF Output 1 |

|

Port 3 |

RF Output 2 |

|

Port 4 |

RF Output 3 |

|

Port 5 |

RF Output 4 |

|

Port 6 |

RF Output 5 |

|

Port 7 |

RF Output 6 |

|

Pin No. |

Description |

Group |

Example 1: Parallel control |

Example 2: RFFE control |

|

1 |

Data1 |

1 |

V1 |

RFFE clock |

|

2 |

Data2 |

V2 |

RFFE data |

|

|

3 |

Data3 |

2 |

V3 |

N/A |

|

4 |

Data4 |

N/A |

N/A |

|

|

5 |

Data5 |

3 |

N/A |

N/A |

|

6 |

Data6 |

N/A |

N/A |

|

|

7 |

Data7 |

4 |

N/A |

N/A |

|

8 |

Data8 |

N/A |

N/A |

|

|

9 |

N/A |

|||

|

10 |

N/A |

|||

|

11 |

N/A |

|||

|

12 |

Vout |

Not be used in this example because this DC voltage cannot be turned off and on quickly. |

||

|

13 |

N/A |

|||

|

14 |

N/A |

|||

|

15 |

GND |

|||

Used for providing Vdd (and Vio for RFFE) in this example. Convertible to BNC connectors by using MCX(f)-BNC(m) cables. (included in M9341B option 001 “Interface cables for M9341B” ).

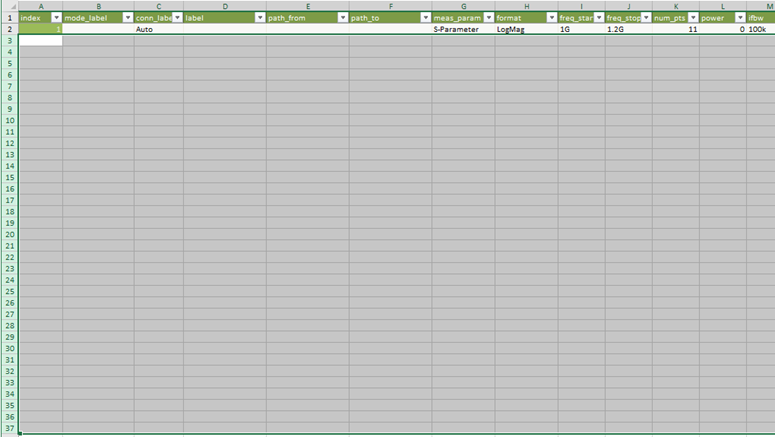

Using Excel template function allows you to create your test plan more easily and quickly when your configuration has many test steps and many parameters for modes and connections. In this example, the setups for Test Step and Mode in test plan is configured on the Excel application using an Excel template.

Launch the AMX Test Plan Builder and File > New

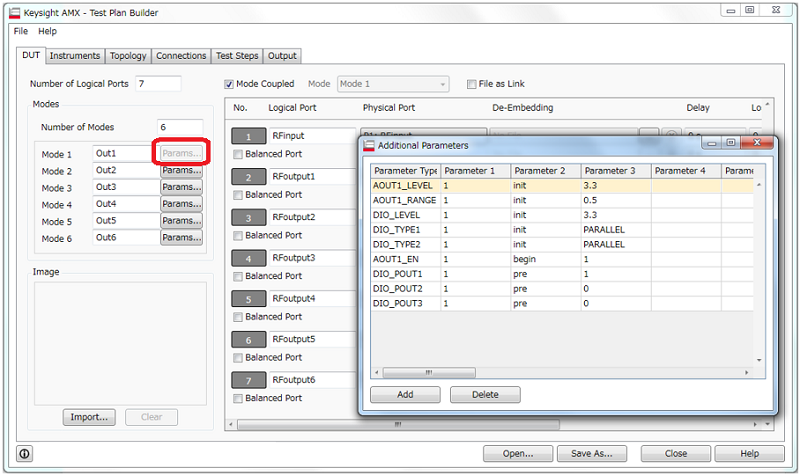

Enter the basic information on the DUT and Instruments, which are required for generating the Excel template in the next step.

|

DUT Tab

|

|

Instrument Tab

|

Open the generated Excel template file by the Excel application.

In the “Spec Sheet” tab, click "B2" cell under "mode_label", then select "Mode1 (Out1) from pull-down menu.

Setup the second row ("B") according to the DUT test conditions, by selecting the items from the pulldown menu or typing the value.

Right-click on any cells in the second row ("B") and select “Insert” > "Table Row Below" from the Excel popup menu. The same pull down menus are available in the inserted row.

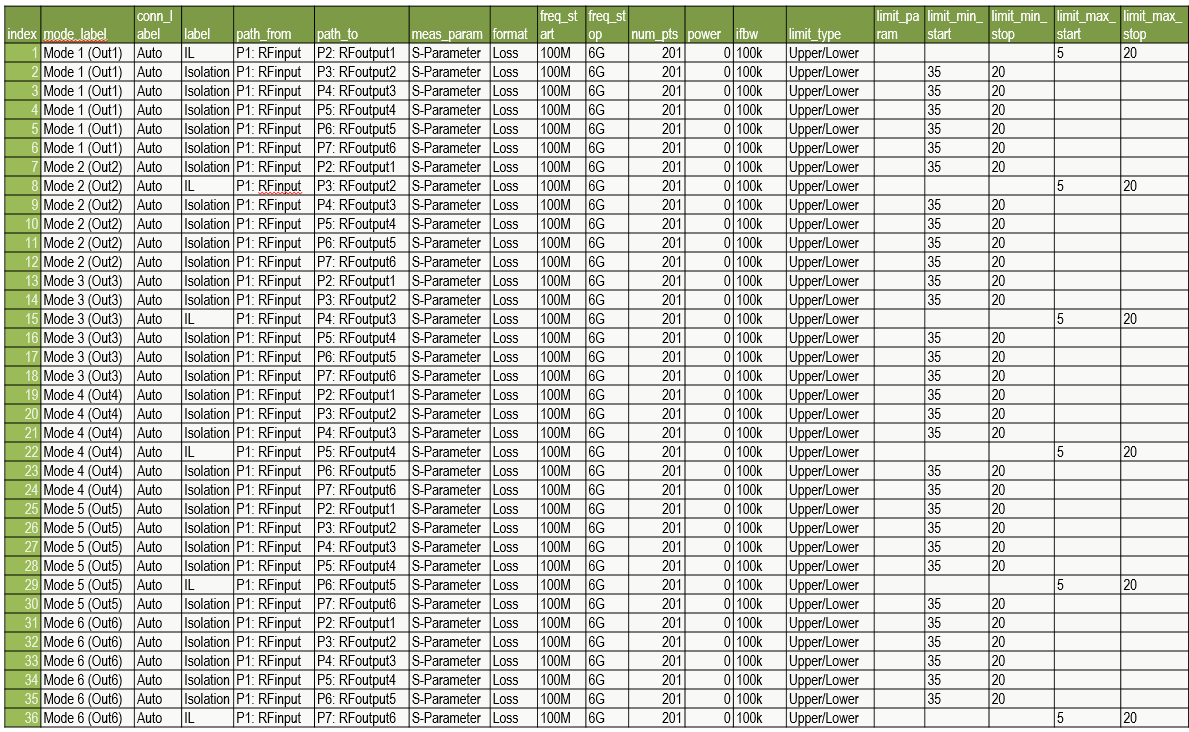

Complete the DUT test conditions and specs as shown below

“Connection_label: Auto” automatically selects an appropriate connection pattern from the ones you have defined in the Test Plan Builder before generating the Excel template. In this example, just one connection pattern “Connection 1” using the calibrated 7 test ports was defined and it will be used for all test items.

When creating the DUT test plan in the Excel template, the prefixes “Mode x:” and “Px:” (x=1, 2, 3…) are added to the labels you defined in the Test Plan Builder.

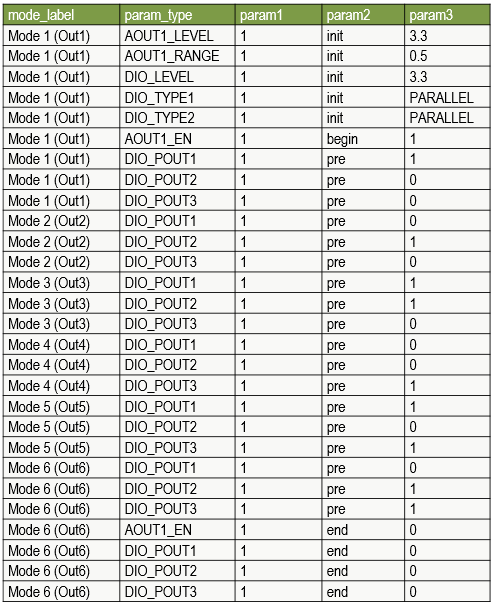

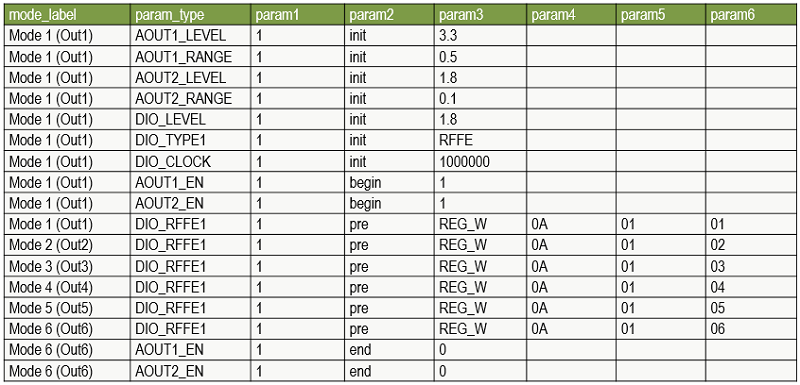

In the “Mode” tab, enter the M9341B control sequence as follows. See the Controlling M9341B I/O Module for the control parameters.

When you complete editing the DUT test plan including the M9341B control sequence, save it as an Excel .xlsx file with your desired filename. This file is for future edit, just in case.

Save this as the XML file by adding “.ss” to the filename, for example, “DUTtestplan.ss.xml”.

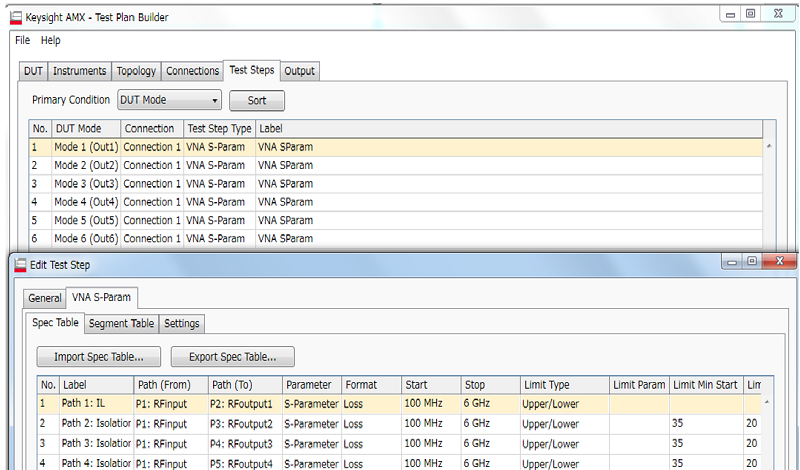

Go back to the Test Steps tab of the AMX Test Plan Builder where you generated the Excel template.

Click [Import Spec Sheet…] and import the ss.xml file you generated. The DUT test plan and the DUT mode control sequence created in the Excel file will be imported to the AMX Test Plan Builder.

Confirm that the information in the Excel file is correctly imported by opening each mode in the Test Steps and DUT tabs.

In the menu bar, select “File” -> “Save As…” and save the test plan file (.tpbproj).

In the Output tab, click [Output Test Plan…] to build and output the TAP test sequence file (.TapPlan) to be executed on the TAP.

Copy the generated TapPlan file to the PXIe controller.

Launch the TAP on the PXIe controller.

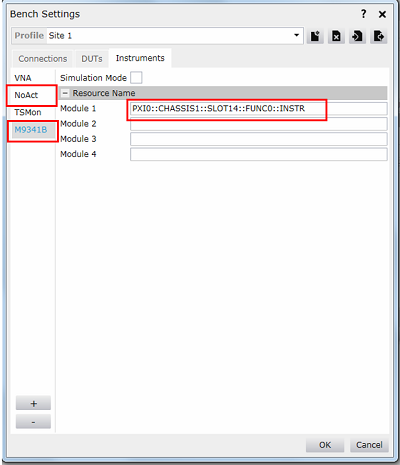

In the menu bar, select “Settings” -> “Bench” -> “Instruments” to open the Bench Settings dialog.

Select the bench profile you are going to use (“Site 1” in this example).

Add “VNA”, “TSMon”, and “No Action” if they are not listed in this dialog.

Delete “DUTMon” if it is listed.

Add “M9341B” and enter the VISA address of the M9341B I/O module. The M9341B’s VISA address can be confirmed by opening the Keysight IO Libraries

Load the .TapPlan file.

Run the TapPlan to execute the initial setup sweep for setting up the VNA.

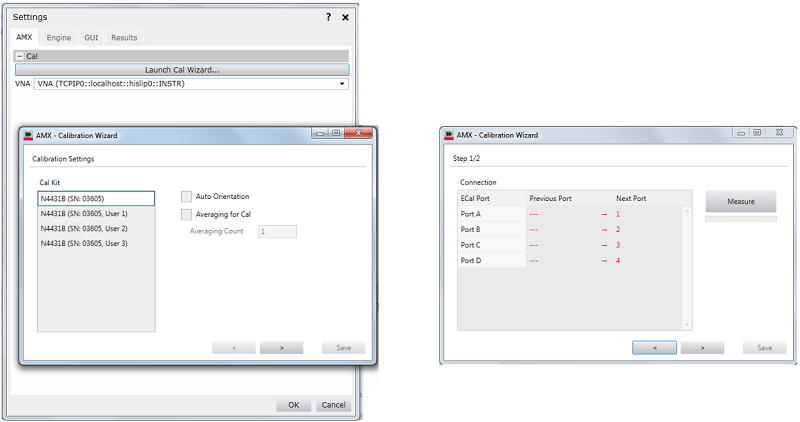

Confirm that the 4-port ECal module is connected to the PXIe controller.

In the menu bar, select “Settings” -> “AMX/AMX” to launch the Cal Wizard. Execute the full 7-port cal by following the guidance.

In the case of test plans consisting of a lot of modes and VNA channels, it is recommended NOT to use the ECal “Auto Orientation” function for faster execution of the Cal Wizard.

Once you complete the calibration with the Cal Wizard, you can skip the setup sweep to shorten the test preparation time from the next time, by checking “Skip Setup” in the “Settings (VNA S-Param)” step.

Connect the DUT to the VNA and M9341B.

Connect the TAP resource by clicking ![]()

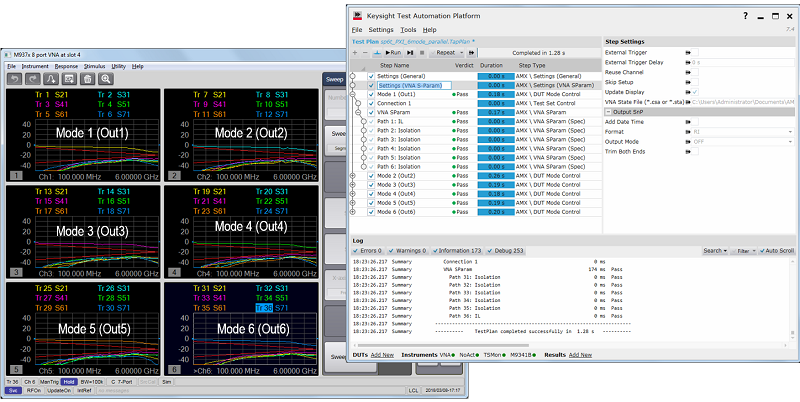

Run the TapPlan to execute the test. Now the DUT test sequence is executed and test results are displayed as shown below