N1076A Optical/Electrical CDR

N1076A optical/electrical clock recovery takes an incoming data or clock signal, locks onto it using a phase-locked loop (PLL) circuit, and outputs a recovered clock. The recovered clock can be used as a timing reference for oscilloscopes (like the N1000A and N1090A, N1092-series, and N1094-series DCA-M oscilloscopes) or BERTS. The N1076A works with both NRZ and PAM4 signals. With optional external hardware equalizers (such as provided in the N1027A-76A kit), you can perform "closed eye" measurements. For installation, safety, and regulatory information, refer to the N107X-series user's guide which can be downloaded from www.keysight.com. Clock recovery is often required for:

N1076A optical/electrical clock recovery takes an incoming data or clock signal, locks onto it using a phase-locked loop (PLL) circuit, and outputs a recovered clock. The recovered clock can be used as a timing reference for oscilloscopes (like the N1000A and N1090A, N1092-series, and N1094-series DCA-M oscilloscopes) or BERTS. The N1076A works with both NRZ and PAM4 signals. With optional external hardware equalizers (such as provided in the N1027A-76A kit), you can perform "closed eye" measurements. For installation, safety, and regulatory information, refer to the N107X-series user's guide which can be downloaded from www.keysight.com. Clock recovery is often required for:

- Standards compliance

- Clock-less devices

- Excessive clock-to-data delay such as is introduced by long spools of fiber-optic cable.

This module requires FlexDCA firmware version A.05.50 or above.

Delay Matching

When using an N1076A, your test setup may require that additional delay be added. This can occur if any of the includes following are true:

- An N1000A-PTB (Internal Precision Time Base) is used.

- An N1076A is used.

- Low frequency jitter in the order of a few 100 fs is present on the signal.

Added delay is not required if your test setup is using an 86107A precision timebase module or an 86108A/B precision waveform analyzer module. A delay-line assembly that adds the required amount of delay is provided in the N1027A-76A electrical clock recovery phase matching kit. This delay-line assembly attaches to the N1000A's rear panel. For instructions on installing the delay line and drawings of example test setups, download the N1076/7A user's guide from keysight.com.

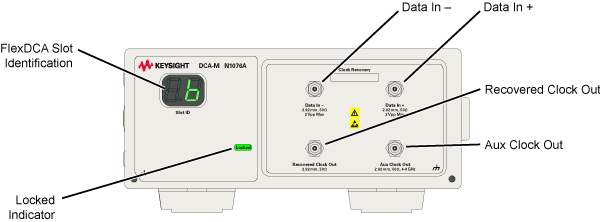

| Indicator | Description |

|---|---|

|

Displays the FlexDCA extended module slot where the N1076A is installed. |

|

Locked light is green when the N1076B is locked on the input signal. |

| Data In – and Data In + port | These are the single-ended and differential data inputs from which to recover the clock. Use a splitter to divert part of the data signal to clock recovery and part of the signal to the oscilloscope's channel input. |

| Recovered Clock Out port | Connect this output to the oscilloscope's clock or trigger input. |

| Aux Clock Out port | An auxilliary recovered clock output from 4 GHz to 8 GHz. |

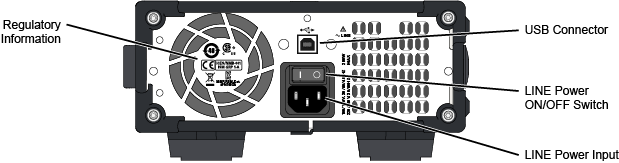

Rear Panel

| Port | Description |

|---|---|

| USB connector | Use the provided USB cable to connect this port to an N1000A's or PC's USB connector. |

| LINE power on/off switch | Use this switch to turn the N1076A on and off. |

| LINE power input | Refer to the N1076A user's guide for LINE power specifications. This book can be downloaded from www.keysight.com. |

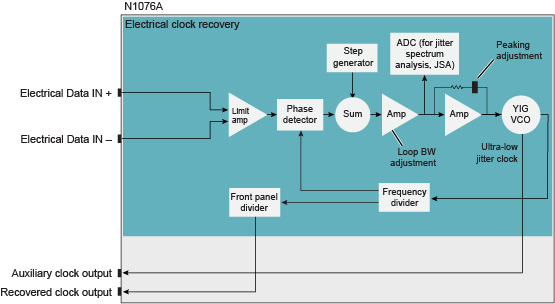

Block Diagram

Automatic Relock

If the clock recovery module loses lock, the trigger becomes asynchronous with the data and the instrument will not display a correctly triggered waveform. By default, when lock is lost, the instrument automatically tries to re-establish lock. Automatic relocking is most helpful when probing a device under test. You can turn off or on automatic relocking from the Clock Recovery setup dialog. Loss of lock, or false lock, conditions may be caused by unusual patterns with a large amount of consecutive 1's or 0's. If the module loses lock during any procedure or measurement, reestablish lock and then repeat the procedure or measurement. For example, if lock is lost while saving a pattern waveform to a file, the data stored in the file will be corrupt.

Locking on the Data Rate

When using the module, you must specify the symbol rate of the clock to be recovered and lock the module on the symbol rate. Under two conditions, the module may lock on a symbol rate other than the specified rate. In the first condition, lock can occur if the entered symbol rate is an integer multiple of the actual symbol rate of the signal. The second condition occurs because the acquisition range is broad (greater than ±5000 PPM). This makes it possible for the module to lock on a signal that is higher or lower than the selected value. For example, if you select a 2.48832 GBd symbol rate but the signal is actually 2.5 GBd, the module may still lock on the signal.

Loop Bandwidth and Jitter

When measuring jitter relative to the recovered clock, jitter that is present on both the data and the recovered clock can not be detected by the instrument. Jitter that is within the clock recovery module's loop bandwidth appears on the recovered clock. Jitter that is outside of the loop bandwidth does not appear on the recovered clock and can be detected on the data.

Specific jitter frequencies in the vicinity of the loop bandwidth may appear amplified or attenuated due to the scope timebase delay and clock recovery group delay. The electrical through-path does not have a delay line. Compensation can be made, by adding an electrical cable between the electrical output and the vertical channel. However, this may affect signal quality.

If the display shows a clock recovery lock lost status message, clock recovery cannot be established on the signal. Make sure that your signal is attached with a power level greater than the minimum (see the specifications) and that the symbol rate is set correctly to within the specified acquisition range.

Features at a Glance

For detailed information, refer to the N1076A specifications help.

| Feature | Partial Specifications |

|---|---|

| Input date rate | |

| Option 216 | 50 MBd to 16 GBd |

| Option 232 | 50 MBd to 32 GBd |

| Minimum input level to acquire lock | |

| Single-ended | 25 mVpp |

| Differential | 50 mVpp |

| Input voltage levels | –2.2V to 3.2V (V/s Vpp, max) |

| Recovered Clock Out | 50 MHz to 16 GHz |

| Aux Clock Out | 4 GHz to 8 GHz 800 mVpp |

| Jitter spectrum analysis (Option JSA) | ♦ |

Available Options

| Option | Description |

|---|---|

| 216 | 50 Mbaud to 16 Gbaud |

| 232 | 50 Mbaud to 32 Gbaud |

| CR1 | Electrical clock-recovery phase matching kit |

| 1CM | Rack-mount kit for a single N1076A |

| 1CN | Rack-mount kit for two N1076As (mounted side-by-side) |