Status Byte Registers

Status Byte Register

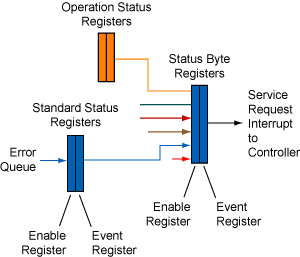

The Status Byte Register is the summary-level register in the status reporting structure. It contains summary bits that monitor activity in the other status registers and queues. The Status Byte Register is a live register. That is, its summary bits are set and cleared by the presence and absence of a summary bit from other event registers or queues. If the Status Byte Register is to be used with the Service Request Enable Register to set bit 6 (RQS/MSS) and to generate an SRQ, at least one of the summary bits must be enabled, then set. Also, event bits in all other status registers must be specifically enabled to generate the summary bit that sets the associated summary bit in the Status Byte Register.

- Use the

*RSTand*CLScommon commands to clear all event registers before you start monitoring FlexOTO. - To generate a service request (SRQ) interrupt to an external computer, enable at least one bit in the Status Byte Enable Register.

- Use the

*ESEcommon command to enable Standard Event Status Register bits to generate a summary bit.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Bit Weight |

128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 |

| Event Register |

OPER | RQS/MSS | ESB | MAV | — | MSG | USR | TRG |

| Enable Register |

Enable and Event Registers

To read the decimal-weighted sum of all set bits in the Status Byte register, use the *STB? common query or a GPIB serial poll command. Here is the difference between the two commands:

- The

*STB?common query reads bit 6 as the Main Summary Status (MSS) and does not clear the bit or have any affect on the SRQ interrupt. It also clears bit 4, the Message Available bit (MAV), if there are no other messages in the Output Queue. - The GPIB serial poll command reads bit 6 as the Request Service (RQS) bit and clears the bit which clears the SRQ interrupt.

Bit 6 (MSS/RQS) was defined to cover all possible computer interfaces, including a computer that could not do a serial poll. The advantage of using a serial poll to clear bit 6 is that this method allows FlexOTO to generate another SRQ interrupt when another enabled event occurs. Serial polling is the preferred method to read the contents of the Status Byte Register because it resets bit 6 and allows the next enabled event that occurs to generate a new SRQ interrupt.

Standard Status Register

The Standard Status Register monitors the following instrument status events. To read and clear the register, use the *ESR? common query.

- Power On (PON)

- Command Error (CME)

- Execution Error (EXE)

- Device Dependent Error (DDE)

- Query Error (QYE)

- Request Control (RQL)

- Operation Complete (OPC)