:STATus Subsystem

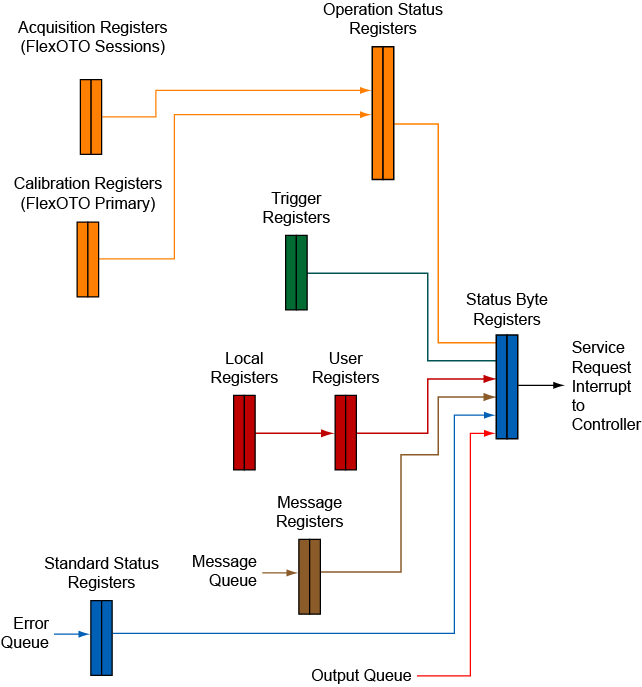

The Status subsystem commands are used to detect when a specific event has occurred. Almost every program that you write will need to monitor FlexOTO for its operational status. This includes querying execution or command errors and determining whether or not measurements have been completed. FlexOTO provides the registers shown in the following Status Reporting Structure picture as its status reporting system. Each register shown in the Status Reporting Structure picture actually represents an event register and an enable register whose output value (True or False) is input to the next downstream register.

All :STATus commands are available in both FlexOTO Hardware Diagram and to FlexOTO Stations modes except for the :STATus:ACQuisition:ENABLE and :STATus:ACQuisition:EVENt commands which are available only in FlexOTO Stations.

Status Reporting Structure (Click the registers in this picture!)

An enable register is a mask for the associated event register. This allows you to activate or deactivate various reporting bits. The :STATus subsystem's commands and queries allow you to monitor the reporting bits from the registers. As shown in the this figure, each bit in an event register is logically AND'ed with its associated bit in the enable register. This allows you the ability to enable or disable reporting of any specific event.

All of the enabled bits are input to an OR gate which allows any enable bit to set the register's output true. The result for each bit is OR'ed to arrive at a true or false output for the register pair. Only if the mask bit is true, will its associated event bit be reported. For example, in this Status Byte Register consider that you only want the status of the USR and OPER bits to be reported. Add the decimal weight for each of these bits *SRE common command), to set the enable register to 130. You have just enabled the USR and OPER events.

The Status Byte and Standard Status registers (shown in blue in the Status Reporting Structure picture) are read by the common commands *STB?, *SRE, *ESR?, and *ESE. In the following picture, you can click on the various registers shown in the following drawing to learn about those registers and the conditions that they monitor.

The Status Byte Register, the Standard Event Status Register group, and the Output Queue are defined as the Standard Status Data Structure Model in IEEE 488.2-1987. IEEE 488.2 defines data structures, commands, and common bit definitions for status reporting. The Operation Status register group are FlexDCA-defined structures and bits.

All of the registers are 16 bit. However, since bits 8 through 16 are seldom used, most register diagrams and tables only show 8 bits. Each register includes an event and an associated enable register represented by the following table. The enable register is a mask that allows you to enable or disable the reporting of specific bits within the associated event register. There is a command to read each event register and read or write each enable register. You can use the event register command to read the contents of the register even when none of the register's summary bits are enabled by the mask to generate an SRQ interrupt. Event register bits that are not enabled still respond to their corresponding conditions. That is, they are set if the corresponding event occurs. However, because they are not enabled, they do not generate a summary bit.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| Bit Weight |

128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 |

| Event Register |

OPER | RQS/MSS | ESB | MAV | — | MSG | USR | TRG |

| Enable Register |

| SCPI Node | FlexOTO |

FlexOTO |

|---|---|---|

:STATus:ACQuisition

|

■ | |

:STATus:CALibration

|

■ | |

:STATus:LOCal

|

■ | ■ |

:STATus:MESSage

|

■ | ■ |

:STATus:OPERation

|

■ | ■ |

:STATus:TRIGger

|

■ | ■ |

:STATus:USER

|

■ | ■ |